This PDF is available from The National Academies Press at http://www.nap.edu/catalog.php?record\_id=12980

| Visit the National Academies Press online and register for    |  |  |

|---------------------------------------------------------------|--|--|

| Instant access to free PDF downloads of titles from the       |  |  |

| NATIONAL ACADEMY OF SCIENCES                                  |  |  |

| NATIONAL ACADEMY OF ENGINEERING                               |  |  |

| INSTITUTE OF MEDICINE                                         |  |  |

| NATIONAL RESEARCH COUNCIL                                     |  |  |

| ✓ 10% off print titles                                        |  |  |

| Custom notification of new releases in your field of interest |  |  |

| Special offers and discounts                                  |  |  |

|                                                               |  |  |

Distribution, posting, or copying of this PDF is strictly prohibited without written permission of the National Academies Press. Unless otherwise indicated, all materials in this PDF are copyrighted by the National Academy of Sciences. Request reprint permission for this book

Copyright © National Academy of Sciences. All rights reserved.

THE NATIONAL ACADEMIES Advisers to the Nation on Science, Engineering, and Medicine

# COMPUTING PERFORMANCE Game Over or Next Level?

Samuel H. Fuller and Lynette I. Millett, Editors

Committee on Sustaining Growth in Computing Performance

Computer Science and Telecommunications Board

Division on Engineering and Physical Science

NATIONAL RESEARCH COUNCIL OF THE NATIONAL ACADEMIES

THE NATIONAL ACADEMIES PRESS Washington, D.C. **www.nap.edu**

Copyright © National Academy of Sciences. All rights reserved.

#### THE NATIONAL ACADEMIES PRESS 500 Fifth Street, N.W. Washington, DC 20001

NOTICE: The project that is the subject of this report was approved by the Governing Board of the National Research Council, whose members are drawn from the councils of the National Academy of Sciences, the National Academy of Engineering, and the Institute of Medicine. The members of the committee responsible for the report were chosen for their special competences and with regard for appropriate balance.

Support for this project was provided by the National Science Foundation under award CNS-0630358. Any opinions, findings, conclusions, or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the organization that provided support for the project.

International Standard Book Number-13: 978-0-309-15951-7 International Standard Book Number-10: 0-309-15951-2 Library of Congress Control Number: 2011923200

Additional copies of this report are available from

The National Academies Press 500 Fifth Street, N.W., Lockbox 285 Washington, D.C. 20055 800 624-6242 202 334-3313 (in the Washington metropolitan area) http://www.nap.edu

Copyright 2011 by the National Academy of Sciences. All rights reserved.

Printed in the United States of America

# THE NATIONAL ACADEMIES

Advisers to the Nation on Science, Engineering, and Medicine

The **National Academy of Sciences** is a private, nonprofit, self-perpetuating society of distinguished scholars engaged in scientific and engineering research, dedicated to the furtherance of science and technology and to their use for the general welfare. Upon the authority of the charter granted to it by the Congress in 1863, the Academy has a mandate that requires it to advise the federal government on scientific and technical matters. Dr. Ralph J. Cicerone is president of the National Academy of Sciences.

The **National Academy of Engineering** was established in 1964, under the charter of the National Academy of Sciences, as a parallel organization of outstanding engineers. It is autonomous in its administration and in the selection of its members, sharing with the National Academy of Sciences the responsibility for advising the federal government. The National Academy of Engineering also sponsors engineering programs aimed at meeting national needs, encourages education and research, and recognizes the superior achievements of engineers. Dr. Charles M. Vest is president of the National Academy of Engineering.

The **Institute of Medicine** was established in 1970 by the National Academy of Sciences to secure the services of eminent members of appropriate professions in the examination of policy matters pertaining to the health of the public. The Institute acts under the responsibility given to the National Academy of Sciences by its congressional charter to be an adviser to the federal government and, upon its own initiative, to identify issues of medical care, research, and education. Dr. Harvey V. Fineberg is president of the Institute of Medicine.

The **National Research Council** was organized by the National Academy of Sciences in 1916 to associate the broad community of science and technology with the Academy's purposes of furthering knowledge and advising the federal government. Functioning in accordance with general policies determined by the Academy, the Council has become the principal operating agency of both the National Academy of Sciences and the National Academy of Engineering in providing services to the government, the public, and the scientific and engineering communities. The Council is administered jointly by both Academies and the Institute of Medicine. Dr. Ralph J. Cicerone and Dr. Charles M. Vest are chair and vice chair, respectively, of the National Research Council.

#### www.national-academies.org

The Future of Computing Performance: Game Over or Next Level?

## COMMITTEE ON SUSTAINING GROWTH IN COMPUTING PERFORMANCE

SAMUEL H. FULLER, Analog Devices Inc., *Chair* LUIZ ANDRÉ BARROSO, Google, Inc. ROBERT P. COLWELL, Independent Consultant WILLIAM J. DALLY, NVIDIA Corporation and Stanford University DAN DOBBERPUHL, P.A. Semi PRADEEP DUBEY, Intel Corporation MARK D. HILL, University of Wisconsin–Madison MARK HOROWITZ, Stanford University DAVID KIRK, NVIDIA Corporation MONICA LAM, Stanford University KATHRYN S. McKINLEY, University of Texas at Austin CHARLES MOORE, Advanced Micro Devices KATHERINE YELICK, University of California, Berkeley

Staff

LYNETTE I. MILLETT, Study Director SHENAE BRADLEY, Senior Program Assistant

### COMPUTER SCIENCE AND TELECOMMUNICATIONS BOARD

ROBERT F. SPROULL, Sun Labs, Chair PRITHVIRAJ BANERJEE, Hewlett Packard Company STEVEN M. BELLOVIN, Columbia University WILLIAM J. DALLY, NVIDIA Corporation and Stanford University SEYMOUR E. GOODMAN, Georgia Institute of Technology JOHN E. KELLY, III, IBM JON M. KLEINBERG, Cornell University ROBERT KRAUT, Carnegie Mellon University SUSAN LANDAU, Radcliffe Institute for Advanced Study PETER LEE, Microsoft Corporation DAVID LIDDLE, US Venture Partners WILLIAM H. PRESS, University of Texas PRABHAKAR RAGHAVAN, Yahoo! Research DAVID E. SHAW, Columbia University ALFRED Z. SPECTOR, Google, Inc. JOHN SWAINSON, Silver Lake Partners PETER SZOLOVITS, Massachusetts Institute of Technology PETER J. WEINBERGER, Google, Inc. ERNEST J. WILSON, University of Southern California

JON EISENBERG, Director RENEE HAWKINS, Financial and Administrative Manager HERBERT S. LIN, Chief Scientist LYNETTE I. MILLETT, Senior Program Officer EMILY ANN MEYER, Program Officer ENITA A. WILLIAMS, Associate Program Officer VIRGINIA BACON TALATI, Associate Program Officer SHENAE BRADLEY, Senior Program Assistant ERIC WHITAKER, Senior Program Assistant

For more information on CSTB, see its website at http://www.cstb.org, write to CSTB, National Research Council, 500 Fifth Street, N.W., Washington, D.C. 20001, call (202) 334-2605, or e-mail the CSTB at cstb@nas.edu.

# Preface

ast, inexpensive computers are now essential for nearly all human endeavors and have been a critical factor in increasing economic productivity, enabling new defense systems, and advancing the frontiers of science. But less well understood is the need for ever-faster computers at ever-lower costs. For the last half-century, computers have been doubling in performance and capacity every couple of years. This remarkable, continuous, exponential growth in computing performance has resulted in an increase by a factor of over 100 per decade and more than a million in the last 40 years. For example, the raw performance of a 1970s supercomputer is now available in a typical modern cell phone. That uninterrupted exponential growth in computing throughout the lifetimes of most people has resulted in the expectation that such phenomenal progress, often called Moore's law, will continue well into the future. Indeed, societal expectations for increased technology performance continue apace and show no signs of slowing, a trend that underscores the need to find ways to sustain exponentially increasing performance in multiple dimensions.

The essential engine that made that exponential growth possible is now in considerable danger. Thermal-power challenges and increasingly expensive energy demands pose threats to the historical rate of increase in processor performance. The implications of a dramatic slowdown in how quickly computer performance is increasing—for our economy, our military, our research institutions, and our way of life—are substantial. That obstacle to continuing growth in computing performance is by now well viii

understood by the designers of microprocessors. Their initial response was to design multiprocessor (often referred to as multicore) chips, but fundamental challenges in algorithm and software design limit the widespread use of multicore systems.

Even as multicore hardware systems are tailored to support software that can exploit multiple computation units, thermal constraints will continue to be a primary concern. It is estimated that data centers delivering Internet services consume over 1.5 percent of U.S. electric power. As the use of the Internet continues to grow and massive computing facilities are demanding that performance keep doubling, devoting corresponding increases in the nation's electrical energy capacity to computing may become too expensive.

We do not have new software approaches that can exploit the innovative architectures, and so sustaining performance growth—and its attendant benefits—presents a major challenge. The present study emerged from discussions among members of the Computer Science and Telecommunications Board and was sponsored by the National Science Foundation. The original statement of task for the Committee on Sustaining Growth in Computing Performance is as follows:

This study will bring together academic and industry researchers, application developers, and members of the user community to explore emerging challenges to sustaining performance growth and meeting expectations in computing across the broad spectrum of software, hardware, and architecture. It will identify key problems along with promising emerging technologies and models and describe how these might fit together over time to enable continued performance scaling. In addition, it will focus attention on areas where there are tractable problems whose solution would have significant payback and at the same time highlight known solutions to challenges that already have them. The study will outline a research, development, and educational agenda for meeting the emerging computing needs of the 21st century.

Parallelism and related approaches in software will increase in importance as a path to achieving continued performance growth. There have been promising developments in the use of parallel processing in some scientific applications, Internet search and retrieval, and the processing of visual and graphic images. This report reviews that progress and recommends subjects for further research and development. Chapter 1 examines the need for high-performance computers, and computers that are increasingly higher-performing, in a variety of sectors of society. The need may be intuitively obvious to some readers but is included here to be explicit about the need for continued performance growth. Chapter 2 examines the aspects of "performance" in depth. Often used as shorthand for speed, performance is actually a much more multidimensional

#### PREFACE

concept. (Appendix A provides a brief history of computing performance as a complement to Chapter 2.) Chapter 3 delves into the fundamental reasons why single-processor performance has stopped its dramatic, exponential growth and why this is a fundamental change rather than a temporary nuisance. Chapter 4 addresses the fundamental challenge now facing the computer science and engineering community: how to exploit parallelism in software and hardware. Chapter 5 outlines the committee's recommended research, practice, and education agenda to meet those challenges.

This report represents the cooperative effort of many people. The members of the study committee, after substantial discussions, drafted and worked though several revisions of the report. We particularly appreciate the insights and perspectives provided by the following experts who briefed the committee:

Jeff Dean, Google, Robert Doering, Texas Instruments, Michael Foster, National Science Foundation, Garth Gibson, Carnegie Mellon University, Wen-Mei Hwu, University of Illinois at Urbana-Champaign, Bruce Jacob, University of Maryland, Jim Larus, Microsoft, Charles Leiserson, Massachusetts Institute of Technology, Trevor Mudge, University of Michigan, Daniel Reed, Microsoft, Phillip Rosedale, Linden Lab, Vivek Sarkar, Rice University, Kevin Skadron, University of Virginia, Tim Sweeny, Epic Games, and Tom Williams, Synopsys.

The committee also thanks the reviewers who provided many perceptive comments that helped to improve the content of the report materially. The committee thanks Michael Marty, who worked with committee member Mark Hill to update some of the graphs, and Paul S. Diette of the Diette Group, who assisted in refining the images. The committee appreciates the financial support provided by the National Science Foundation. The committee also gratefully acknowledges the assistance of members of the National Research Council staff. Lynette Millett, our study director, ably served the critical roles of study organizer, report editor, and review coordinator. Jon Eisenberg provided many valuable suggestions that improved the quality of the final report.

It is difficult to overstate the importance of ever-more-capable com-

х

puters to the U.S. industrial and social infrastructure, economy, and national security. The United States cannot afford to let this growth engine stall out, and a concerted effort is needed to sustain it. Several centers for parallel computing have already been established in leading research universities. Those centers are a good start, and additional, strong actions are required in many subdisciplines of computer science and computer engineering. Our major goal for this study is to help to identify the actions and opportunities that will prove most fruitful.

> Samuel H. Fuller, *Chair* Committee on Sustaining Growth in Computing Performance

# Acknowledgment of Reviewers

This report has been reviewed in draft form by individuals chosen for their diverse perspectives and technical expertise, in accordance with procedures approved by the National Research Council's (NRC's) Report Review Committee. The purpose of this independent review is to provide candid and critical comments that will assist the institution in making its published report as sound as possible and to ensure that the report meets institutional standards for objectivity, evidence, and responsiveness to the study charge. The review comments and draft manuscript remain confidential to protect the integrity of the deliberative process. We wish to thank the following individuals for their review of this report:

Tilak Agerwala, IBM Research, David Ceperley, University of Illinois, Robert Dennard, IBM Research, Robert Doering, Texas Instruments, Inc., Urs Hölzle, Google, Inc., Norm Jouppi, Hewlett-Packard Laboratories, Kevin Kahn, Intel Corporation, James Kajiya, Microsoft Corporation Randy Katz, University of California, Berkeley, Barbara Liskov, Massachusetts Institute of Technology, Keshav Pingali, University of Texas, Austin, James Plummer, Stanford University, and Vivek Sarkar, Rice University.

xi

xii

Although the reviewers listed above have provided many constructive comments and suggestions, they were not asked to endorse the conclusions or recommendations, nor did they see the final draft of the report before its release. The review of this report was overseen by Butler Lampson, Microsoft Corporation. Appointed by the National Research Council, he was responsible for making certain that an independent examination of this report was carried out in accordance with institutional procedures and that all review comments were carefully considered. Responsibility for the final content of this report rests entirely with the authoring committee and the institution.

# Contents

| AB  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| SUI | MMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

| 1   | <ul> <li>THE NEED FOR CONTINUED PERFORMANCE GROWTH</li> <li>Why Faster Computers Are Important, 22</li> <li>The Importance of Computing Performance for the Sciences, 29</li> <li>The Importance of Computing Performance for Defense and National Security, 36</li> <li>The Importance of Computing Performance for Consumer Needs and Applications, 44</li> <li>The Importance of Computing Performance for Enterprise Productivity, 47</li> </ul> | 21         |

| 2   | WHAT IS COMPUTER PERFORMANCE?<br>Why Performance Matters, 58<br>Performance as Measured by Raw Computation, 59<br>Computation and Communication's Effects on Performance, 62<br>Technology Advances and the History of Computer Performance,<br>Assessing Performance with Benchmarks, 68<br>The Interplay of Software and Performance, 70<br>The Economics of Computer Performance, 75                                                              | 53<br>, 65 |

xiii

| xiv         | , C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CONTENTS                |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

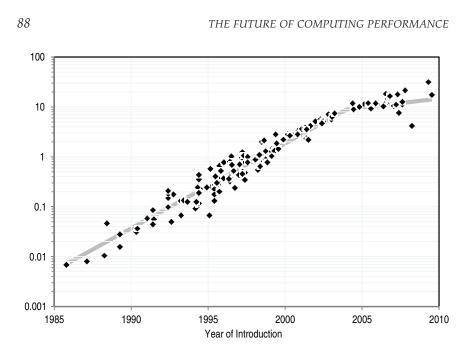

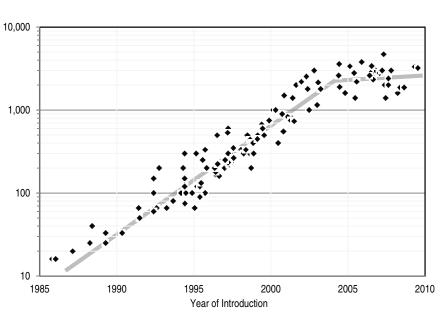

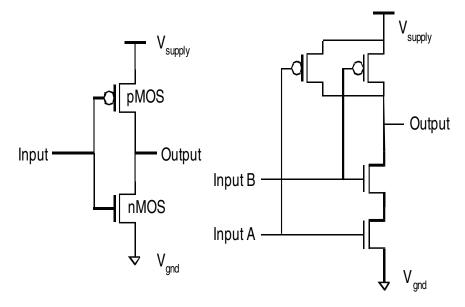

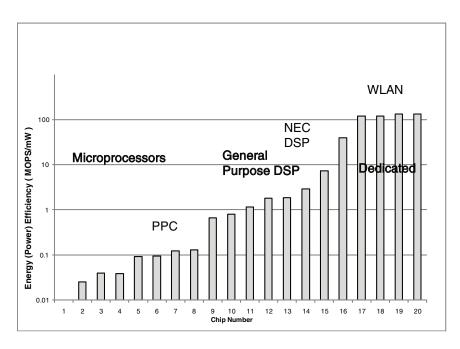

| 3           | <ul> <li>POWER IS NOW LIMITING GROWTH IN COMPUTING<br/>PERFORMANCE</li> <li>Basic Technology Scaling, 83</li> <li>Classic CMOS Scaling, 84</li> <li>How CMOS-Processor Performance Improved Exponentiall<br/>and Then Slowed, 87</li> <li>How Chip Multiprocessors Allow Some Continued<br/>Performance-Scaling, 90</li> <li>Problems in Scaling Nanometer Devices, 94</li> <li>Advanced Technology Options, 97</li> <li>Application-Specific Integrated Circuits, 100</li> <li>Bibliography, 103</li> </ul> | 80<br>y,                |  |  |

| 4           | THE END OF PROGRAMMING AS WE KNOW IT<br>Moore's Bounty: Software Abstraction, 106<br>Software Implications of Parallelism, 110<br>The Challenges of Parallelism, 116<br>The State of the Art of Parallel Programming, 119<br>Parallel-Programming Systems and the Parallel<br>Software "Stack," 127<br>Meeting the Challenges of Parallelism, 130                                                                                                                                                            | 105                     |  |  |

| 5           | RESEARCH, PRACTICE, AND EDUCATION TO MEET<br>TOMORROW'S PERFORMANCE NEEDS<br>Systems Research and Practice, 133<br>Parallel-Programming Models and Education, 146<br>Game Over or Next Level? 150                                                                                                                                                                                                                                                                                                            | 132                     |  |  |

| APPENDIXES  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |  |  |

| A<br>B<br>C | A History of Computer Performance<br>Biographies of Committee Members and Staff<br>Reprint of Gordon E. Moore's "Cramming More Componen<br>onto Integrated Circuits"                                                                                                                                                                                                                                                                                                                                         | 155<br>160<br>ts<br>169 |  |  |

| D           | Reprint of Robert H. Dennard's "Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions"                                                                                                                                                                                                                                                                                                                                                                                                        | 174                     |  |  |

# Abstract

Information technology (IT) has the potential to continue to dramatically transform how we work and live. One might expect that future IT advances will occur as a natural continuation of the stunning advances that IT has enabled over the last half-century, but reality is more sobering.

IT advances of the last half-century have depended critically on the rapid growth of single-processor performance—by a factor of 10,000 in just the last 2 decades-at ever-decreasing cost and with manageable increases in power consumption. That growth stemmed from increasing the number and speed of transistors on a processor chip by reducing their size and—with improvements in memory, storage, and networking capacities—resulted in ever more capable computer systems. It was important for widespread IT adoption that the phenomenal growth in performance was achieved while maintaining the sequential stored-program model that was developed for computers in the 1940s. Moreover, computer manufacturers worked to ensure that specific instruction set compatibility was maintained over generations of computer hardware-that is, a new computer could run new applications, and the existing applications would run faster. Thus, software did not have to be rewritten for each hardware generation, and so ambition and imagination were free to drive the creation of increasingly innovative, capable, and computationally intensive software, and this in turn inspired businesses, government, and the average consumer to buy successive generations of computer software and hardware. Software and hardware advances fed each other, creating a virtuous IT economic cycle.

2

Early in the 21st century, improvements in single-processor performance slowed, as measured in instructions executed per second, and such performance now improves at a very modest pace, if at all. This abrupt shift is due to fundamental limits in the power efficiency of complementary metal oxide semiconductor integrated circuits (used in virtually all computer chips today) and apparent limits in the efficiencies that can be exploited in single-processor architectures. Reductions in transistor size continue apace, and so more transistors can still be packed onto chips, albeit without the speedups seen in the past. As a result, the computerhardware industry has commenced building chips with multiple processors. Current chips range from several complex processors to hundreds of simpler processors, and future generations will keep adding more. Unfortunately, that change in hardware requires a concomitant change in the software programming model. To use chip multiprocessors, applications must use a *parallel programming model*, which divides a program into parts that are then executed in parallel on distinct processors. However, much software today is written according to a sequential programming model, and applications written this way cannot easily be sped up by using parallel processors.

The only foreseeable way to continue advancing performance is to match parallel hardware with parallel software and ensure that the new software is portable across generations of parallel hardware. There has been genuine progress on the software front in specific fields, such as some scientific applications and commercial searching and transactional applications. Heroic programmers can exploit vast amounts of parallelism, domain-specific languages flourish, and powerful abstractions hide complexity. However, none of those developments comes close to the ubiquitous support for programming parallel hardware that is required to ensure that IT's effect on society over the next two decades will be as stunning as it has been over the last half-century.

For those reasons, the Committee on Sustaining Growth in Computing Performance recommends that our nation place a much greater emphasis on IT and computer-science research and development focused on improvements and innovations in parallel processing, and on making the transition to computing centered on parallelism. The following should have high priority:

- Algorithms that can exploit parallel processing; New computing "stacks" (applications, programming languages, compilers, runtime/virtual machines, operating systems, and architectures) that execute parallel rather than sequential programs and that effectively manage software parallelism, hardware parallelism, power, memory, and other resources;

#### ABSTRACT

- Portable programming models that allow expert and typical programmers to express parallelism easily and allow software to be efficiently reused on multiple generations of evolving hardware;

- Parallel-computing architectures driven by applications, including enhancements of chip multiprocessors, conventional dataparallel architectures, application-specific architectures, and radically different architectures;

- Open interface standards for parallel programming systems that promote cooperation and innovation to accelerate the transition to practical parallel computing systems; and

- Engineering and computer-science educational programs that incorporate an increased emphasis on parallelism and use a variety of methods and approaches to better prepare students for the types of computing resources that they will encounter in their careers.

Although all of those areas are important, fundamental power and energy constraints mean that even the best efforts might not yield a complete solution. Parallel computing systems will grow in performance over the long term only if they can become more power-efficient. Therefore, in addition to a focus on parallel processing, we need research and development on much more power-efficient computing systems at all levels of technology, including devices, hardware architecture, and software systems. The Future of Computing Performance: Game Over or Next Level?

# Summary

The end of dramatic exponential growth in single-processor performance marks the end of the dominance of the single microprocessor in computing. The era of sequential computing must give way to a new era in which parallelism is at the forefront. Although important scientific and engineering challenges lie ahead, this is an opportune time for innovation in programming systems and computing architectures. We have already begun to see diversity in computer designs to optimize for such considerations as power and throughput. The next generation of discoveries is likely to require advances at both the hardware and software levels of computing systems.

There is no guarantee that we can make parallel computing as common and easy to use as yesterday's sequential single-processor computer systems, but unless we aggressively pursue efforts suggested by the recommendations below, it will be "game over" for growth in computing performance. If parallel programming and related software efforts fail to become widespread, the development of exciting new applications that drive the computer industry will stall; if such innovation stalls, many other parts of the economy will follow suit.

This report of the Committee on Sustaining Growth in Computing Performance describes the factors that have led to the future limitations on growth for single processors based on complementary metal oxide semiconductor (CMOS) technology. The recommendations that follow are aimed at supporting and focusing research, development, and educa6

tion in parallel computing, architectures, and power to sustain growth in computer performance and enjoy the next level of benefits to society.

### SOCIETAL DEPENDENCE ON GROWTH IN COMPUTING PERFORMANCE

Information technology (IT) has transformed how we work and live and has the potential to continue to do so. IT helps to bring distant people together, coordinate disaster response, enhance economic productivity, enable new medical diagnoses and treatments, add new efficiencies to our economy, improve weather prediction and climate modeling, broaden educational access, strengthen national defense, advance science, and produce and deliver content for education and entertainment.

Those transformations have been made possible by sustained improvements in the performance of computers. We have been living in a world where the cost of information processing has been decreasing exponentially year after year. The term *Moore's law*, which originally referred to an empirical observation about the most economically favorable rate for industry to increase the number of transistors on a chip, has come to be associated, at least popularly, with the expectation that microprocessors will become faster, that communication bandwidth will increase, that storage will become less expensive, and, more broadly, that computers will become faster. Most notably, the performance of individual computer processors increased on the order of 10,000 times over the last 2 decades of the 20th century without substantial increases in cost or power consumption.

Although some might say that they do not want or need a faster computer, computer users as well as the computer industry have in reality become dependent on the continuation of that performance growth. U.S. leadership in IT depends in no small part on taking advantage of the leading edge of computing performance. The IT industry annually generates a trillion dollars of revenue and has even larger indirect effects throughout society. This huge economic engine depends on a sustained demand for IT products and services; use of these products and services in turn fuels demand for constantly improving performance. More broadly, virtually every sector of society-manufacturing, financial services, education, science, government, the military, entertainment, and so on-has become dependent on continued growth in computing performance to drive industrial productivity, increase efficiency, and enable innovation. The performance achievements have driven an implicit, pervasive expectation that future IT advances will occur as an inevitable continuation of the stunning advances that IT has experienced over the last half-century.

Finding: The information technology sector itself and most other sectors of society—for example, manufacturing, financial and other services, science, engineering, education, defense and other government services, and entertainment—have grown dependent on continued growth in computing performance.

Software developers themselves have come to depend on that growth in performance in several important ways, including:

- Developing applications that were previously infeasible, such as real-time video chat;

- Adding visible features and ever more sophisticated interfaces to existing applications;

- Adding "hidden" (nonfunctional) value—such as improved security, reliability, and other trustworthiness features—without degrading the performance of existing functions;

- Using higher-level abstractions, programming languages, and systems that require more computing power but reduce development time and improve software quality by making the development of correct programs and the integration of components easier; and

- Anticipating performance improvements and creating innovative, computationally intensive applications even before the required performance is available at low cost.

The U.S. computing industry has been adept at taking advantage of increases in computing performance, allowing the United States to be a moving and therefore elusive target—innovating and improvising faster than anyone else. If computer capability improvements stall, the U.S. lead will erode, as will the associated industrial competitiveness and military advantage.

Another consequence of 5 decades of exponential growth in performance has been the rise and dominance of the general-purpose microprocessor that is the heart of all personal computers. The dominance of the general-purpose microprocessor has stemmed from a virtuous cycle of (1) economies of scale wherein each generation of computers has been both faster and less expensive than the previous one, and (2) software correctness and performance portability—current software continues to run and to run faster on the new computers, and innovative applications can also run on them. The economies of scale have resulted from Moore's law scaling of transistor density along with innovative approaches to harnessing effectively all the new transistors that have become available. Portability has been preserved by keeping instruction sets compatible over many THE FUTURE OF COMPUTING PERFORMANCE

generations of microprocessors even as the underlying microprocessor technology saw substantial enhancements, allowing investments in software to be amortized over long periods.

The success of this virtuous cycle dampened interest in the development of alternative computer and programming models. Even though alternative architectures might have been technically superior (faster or more power-efficient) in specific domains, if they did not offer software compatibility they could not easily compete in the marketplace and were easily overtaken by the ever-improving general-purpose processors available at a relatively low cost.

### CONSTRAINTS ON GROWTH IN SINGLE-PROCESSOR PERFORMANCE

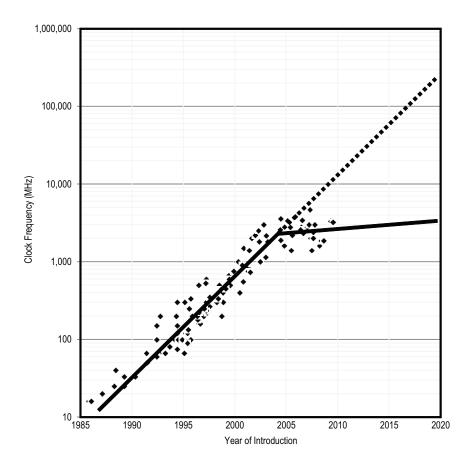

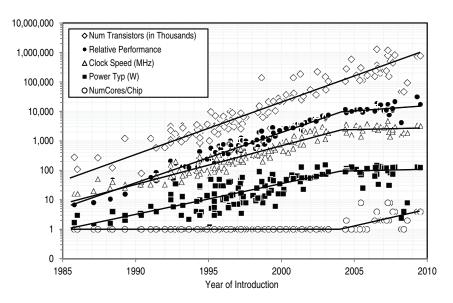

By the 2000s, however, it had become apparent that processor performance growth was facing two major constraints. First, the ability to increase clock speeds has run up against power limits. The densest, highest-performance, and most power-efficient integrated circuits are constructed from CMOS technology. By 2004, the long-fruitful strategy of scaling down the size of CMOS circuits, reducing the supply voltage and increasing the clock rate was becoming infeasible. Since a chip's power consumption is proportional to the clock speed times the supply voltage squared, the inability to continue to lower the supply voltage halted the ability to increase the clock speed without increasing power dissipation. The resulting power consumption exceeded the few hundred watts per chip level that can practically be dissipated in a mass-market computing device as well as the practical limits for mobile, battery-powered devices. The ultimate consequence has been that growth in single-processor performance has stalled (or at least is being increased only marginally over time).

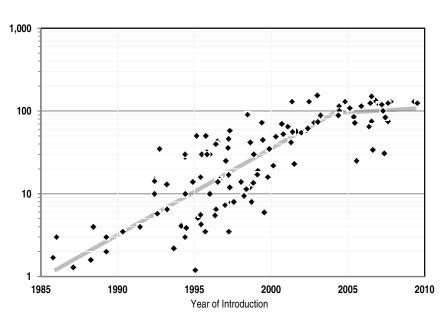

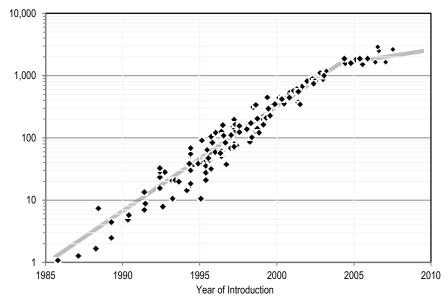

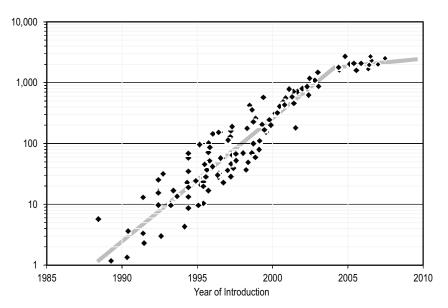

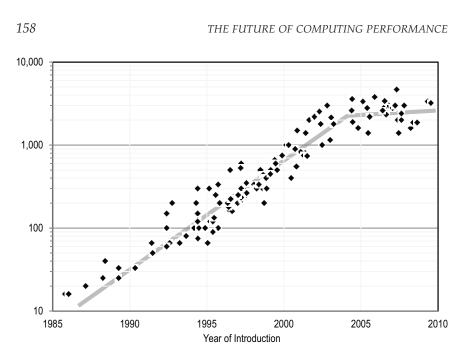

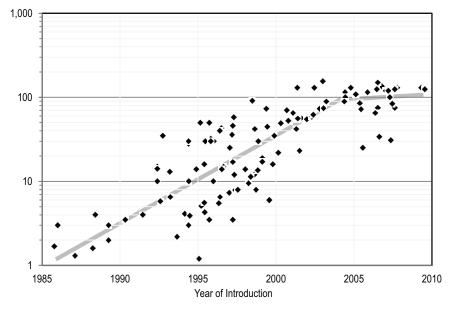

Second, efforts to improve the internal architecture of individual processors have seen diminishing returns. Many advances in the architecture of general-purpose sequential processors, such as deeper pipelines and speculative execution, have contributed to successful exploitation of increasing transistor densities. Today, however, there appears to be little opportunity to significantly increase performance by improving the internal structure of existing sequential processors. Figure S.1 graphically illustrates these trends and the slowdown in the growth of processor performance, clock speed, and power since around 2004. In contrast, it also shows the continued, exponential growth in the number of transistors per chip. The original Moore's law projection of increasing transistors per chip continues unabated even as performance has stalled. The 2009 edition of

8

FIGURE S.1 Processor performance from 1986 to 2008 as measured by the benchmark suite SPECint2000 and consensus targets from the International Technology Roadmap for Semiconductors for 2009 to 2020. The vertical scale is logarithmic. A break in the growth rate at around 2004 can be seen. Before 2004, processor performance was growing by a factor of about 100 per decade; since 2004, processor performance has been growing and is forecasted to grow by a factor of only about 2 per decade. An expectation gap is apparent. In 2010, this expectation gap for single-processor performance is about a factor of 10; by 2020, it will have grown to a factor of 1,000. Most sectors of the economy and society implicitly or explicitly expect computing to deliver steady, exponentially increasing performance, but as these graphs illustrate, traditional single-processor computing systems will not match expectations. Note that the SPEC benchmarks are a set of artificial workloads intended to measure a computer system's speed. A machine that achieves a SPEC benchmark score that is 30 percent faster than that of another machine should feel about 30 percent faster than the other machine on real workloads. 10

the International Technology Roadmap for Semiconductors (ITRS)<sup>1</sup> predicts the continued growth of transistors/chips for the next decade, but it will probably not be possible to continue to increase the transistor density (number of transistors per unit area) of CMOS chips at the current pace beyond the next 10 to 15 years. Figure S.1 shows the historical growth in single-processor performance and a forecast of processor performance to 2020 based on the ITRS roadmap. A dashed line represents what could have been expected if single-processor performance had continued on its historical trend. By 2020, however, a large "expectation gap" is apparent for single processors. This report explores the implications of that gap and offers a way to begin to bridging it.

# Finding: After many decades of dramatic exponential growth, singleprocessor performance is increasing at a much lower rate, and this situation is not expected to improve in the foreseeable future.

Energy and power constraints play an important—and growing—role in computing performance. Computer systems require energy to operate and, as with any device, the more energy needed, the more expensive the system is to operate and maintain. Moreover, all the energy consumed by the system ends up as heat, which must be removed. Even when new parallel models and solutions are found, most future computing systems' performance will be limited by power or energy in ways that the computer industry and researchers have not had to deal with thus far. For example, the benefits of replacing a single, highly complex processor with increasing numbers of simpler processors will eventually reach a limit when further simplification costs more in performance than it saves in power. Constraints due to power are thus inevitable for systems ranging from hand-held devices to the largest computing data centers even as the transition is made to parallel systems.

Even with success in sidestepping the limits on single-processor performance, total energy consumption will remain an important concern, and growth in performance will become limited by power consumption within a decade. The total energy consumed by computing systems is already substantial and continues to grow rapidly in the United States and around the world. As is the case in other sectors of the economy, the total energy consumed by computing will come under increasing pressure.

<sup>&</sup>lt;sup>1</sup>ITRS, 2009, ITRS 2009 Edition, available online at http://www.itrs.net/links/2009ITRS/ Home2009.htm.

Finding: The growth in the performance of computing systems—even if they are multiple-processor parallel systems—will become limited by power consumption within a decade.

In short, the single processor and the sequential programming model that have dominated computing since its birth in the 1940s, will no longer be sufficient to deliver the continued growth in performance needed to facilitate future IT advances.<sup>2</sup> Moreover, it is an open question whether power and energy will be showstoppers or just significant constraints. Although these issues pose major technical challenges, they will also drive considerable innovation in computing by forcing a rethinking of the von Neumann model that has prevailed since the 1940s.

### PARALLELISM AS A SOLUTION

Future growth in computing performance will have to come from parallelism. Most software developers today think and program by using a sequential programming model to create software for single generalpurpose microprocessors. The microprocessor industry has already begun to deliver parallel hardware in mainstream products with chip multiprocessors (CMPs-sometimes referred to as multicore), an approach that places new burdens on software developers to build applications to take advantage of multiple, distinct cores. Although developers have found reasonable ways to use two or even four cores effectively by running independent tasks on each one, they have not, for the most part, parallelized individual tasks in such a way as to make full use of the available computational capacity. Moreover, if industry continues to follow the same trends, they will soon be delivering chips with hundreds of cores. Harnessing these cores will require new techniques for parallel computing, including breakthroughs in software models, languages, and tools. Developers of both hardware and software will need to focus more attention on overall system performance, likely at the expense of time to market and the efficiency of the virtuous cycle described previously.

Of course, the computer science and engineering communities have been working for decades on the hard problems associated with parallelism. For example, high-performance computing for science and engineering applications has depended on particular parallel-programming techniques such as Message Passing Interface (MPI). In other cases,

<sup>&</sup>lt;sup>2</sup>Of course, computing performance encompasses more than intrinsic CPU speed, but CPU performance has historically driven everything else: input/output, memory sizes and speeds, buses and interconnects, networks, and so on. If continued growth in CPU performance is threatened, so are the rest.

#### THE FUTURE OF COMPUTING PERFORMANCE

domain-specific languages and abstractions such as MapReduce have provided interfaces with behind-the-scenes parallelism and well-chosen abstractions developed by experts, technologies that hide the complexity of parallel programming from application developers. Those efforts have typically involved a small cadre of programmers with highly specialized training in parallel programming working on relatively narrow types of computing problems. None of this work has, however, come close to enabling widespread use of parallel programming for a wide array of computing problems.

Encouragingly, a few research universities, including MIT, the University of Washington, the University of California, Berkeley, and others have launched or revived research programs in parallelism, and the topic has also seen a renewed focus in industry at companies such as NVIDIA. However, these initial investments are not commensurate with the magnitude of the technical challenges or the stakes. Moreover, history shows that technology advances of this sort often require a decade or more. The results of such research are already needed today to sustain historical trends in computing performance, which makes us already a decade behind. Even with concerted investment, there is no guarantee that widely applicable solutions will be found. If they cannot be, we need to know that as soon as possible so that we can seek other avenues for progress.

Finding: There is no known alternative to parallel systems for sustaining growth in computing performance; however, no compelling programming paradigms for general parallel systems have yet emerged.

### RECOMMENDATIONS

The committee's findings outline a set of serious challenges that affect not only the computing industry but also the many sectors of society that now depend on advances in IT and computation, and they suggest national and global economic repercussions. At the same time, the crisis in computing performance has pointed the way to new opportunities for innovation in diverse software and hardware infrastructures that excel in metrics other than single-chip processing performance, such as low power consumption and aggregate delivery of throughput cycles. There are opportunities for major changes in system architectures, and extensive investment in whole-system research is needed to lay the foundation of the computing environment for the next generation.

The committee's recommendations are broadly aimed at federal research agencies, the computing and information technology industry,

12

and educators and fall into two categories. The first is research. The best science and engineering minds must be brought to bear on the challenges. The second is practice and education. Better practice in the development of computer hardware and software *today* will provide a foundation for future performance gains. Education will enable the emerging generation of technical experts to understand different and in some cases not-yet-developed parallel models of thinking about IT, computation, and software.

### **Recommendations for Research**

The committee urges investment in several crosscutting areas of research, including algorithms, broadly usable parallel programming methods, rethinking the canonical computing stack, parallel architectures, and power efficiency.

# Recommendation: Invest in research in and development of algorithms that can exploit parallel processing.

Today, relatively little software is explicitly parallel. To obtain the desired performance, it will be necessary for many more—if not most—software designers to grapple with parallelism. For some applications, they may still be able to write sequential programs, leaving it to compilers and other software tools to extract the parallelism in the underlying algorithms. For more complex applications, it may be necessary for programmers to write explicitly parallel programs. Parallel approaches are already used in some applications when there is no viable alternative. The committee believes that careful attention to parallelism will become the rule rather than the notable exception.

## Recommendation: Invest in research in and development of programming methods that will enable efficient use of parallel systems not only by parallel-systems experts but also by typical programmers.

Many of today's programming models, languages, compilers, hypervisors (to manage virtual machines), and operating systems are targeted primarily at single-processor hardware. In the future, these layers will need to target, optimize programs for, and be optimized themselves for explicitly parallel hardware. The intellectual keystone of the endeavor is rethinking programming models so that programmers can express application parallelism naturally. The idea is to allow parallel software to be developed for diverse systems rather than specific configurations, and to have system software deal with balancing computation and minimizing communication among multiple computational units. The situation is reminiscent of the late 1970s, when programming models and tools were not up to the task of building substantially more complex software. Better programming models—such as structured programming in the 1970s, object orientation in the 1980s, and managed programming languages in the 1990s—have made it possible to produce much more sophisticated software. Analogous advances in the form of better tools and additional training will be needed to increase programmer productivity for parallel systems.

A key breakthrough would be the ability to express application parallelism in such ways that an application will run faster as more cores are added. The most prevalent parallel-programming languages do not provide this performance portability. A related question is what to do with the enormous body of legacy sequential code, which will be able to realize substantial performance improvements only if it can be parallelized. Experience has shown that parallelizing sequential code or highly sequential algorithms effectively is exceedingly difficult in general. Writing software that expresses the type of parallelism required to exploit chip multiprocessor hardware requires new software engineering processes and tools, including new programming languages that ease the expression of parallelism and a new software stack that can exploit and map the parallelism to hardware that is diverse and evolving. It will also require training programmers to solve their problems with parallel computational thinking.

The models themselves may or may not be explicitly parallel; it is an open question whether or when most programmers should be exposed to explicit parallelism. A single, universal programming model may or may not exist, and so multiple models—including some that are domainspecific—should be explored. Additional research is needed in the development of new libraries and new programming languages with appropriate compilation and runtime support that embody the new programming models. It seems reasonable to expect that some programming models, libraries, and languages will be suited for a broad base of skilled but not superstar programmers. They may even appear on the surface to be sequential or declarative. Others, however, will target efficiency, seeking the highest performance for critical subsystems that are to be extensively reused, and thus be intended for a smaller set of expert programmers.

Another focus for research should be system software for highly parallel systems. Although operating systems of today can handle some modest parallelism, future systems will include many more processors whose allocation, load balancing, and data communication and synchronization interactions will be difficult to handle well. Solving those problems will require a rethinking of how computation and communication resources

14

are viewed much as demands for increased memory size led to the introduction of virtual memory a half-century ago.

# Recommendation: Focus long-term efforts on rethinking of the canonical computing "stack"—applications, programming language, compiler, runtime, virtual machine, operating system, hypervisor, and architecture—in light of parallelism and resource-management challenges.

Computer scientists and engineers typically manage complexity by separating interface from implementation. In conventional computer systems, that is done recursively to form a computing stack: applications, programming language, compiler, runtime, virtual machine, operating system, hypervisor, and architecture. It is unclear whether today's conventional stack provides the right framework to support parallelism and manage resources. The structure and elements of the stack itself should be a focus of long-term research exploration.

## Recommendation: Invest in research on and development of parallel architectures driven by applications, including enhancements of chip multiprocessor systems and conventional data-parallel architectures, cost-effective designs for application-specific architectures, and support for radically different approaches.

In addition to innovation and advancements in parallel programming models and systems, advances in architecture and hardware will play an important role. One path forward is to continue to refine the chip multiprocessors (CMPs) and associated architectural approaches. Are today's CMP approaches suitable for designing most computers? The current CMP architecture has the advantage of maintaining compatibility with existing software, the heart of the architectural franchise that keeps companies investing heavily. But CMP architectures bring their own challenges. Will large numbers of cores work in most computer deployments, such as on desktops and even in mobile phones? How can cores be harnessed together temporarily, in an automated or semiautomated fashion, to overcome sequential bottlenecks? What mechanisms and policies will best exploit locality (keeping data stored close to other data that might be needed at the same time or for particular computations and saving on the power needed to move data around) so as to avoid communications bottlenecks? How should synchronization and scheduling be handled? How should challenges associated with power and energy be addressed? What do the new architectures mean for such system-level features as reliability and security?

Is using homogeneous processors in CMP architectures the best

#### THE FUTURE OF COMPUTING PERFORMANCE

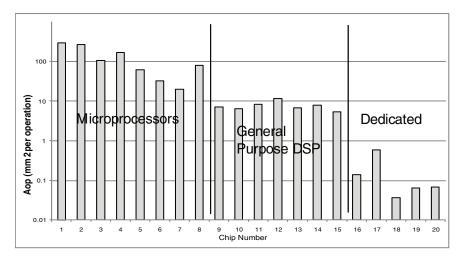

approach, or will computer architectures that include multiple but heterogeneous cores—some of which may be more capable than others or even use different instruction-set architectures—be more effective? Specialpurpose processors that have long exploited parallelism, notably graphics processing units (GPUs) and digital signal processor (DSP) hardware, have been successfully deployed in important segments of the market. Are there other important niches like those filled by GPUs and DSPs? Alternatively, will computing cores support more graphics and GPUs support more general-purpose programs, so that the difference between the two will blur?

Perhaps some entirely new architectural approach will prove more successful. If systems with CMP architectures cannot be effectively programmed, an alternative will be needed. Work in this general area could eschew conventional cores. It can view the chip as a *tabula rasa* of billions of transistors, which translates to hundreds of functional units; the effective organization of those units into a programmable architecture is an open question. Exploratory computing systems based on field-programmable gate arrays (FPGAs) are a step in this direction, but continued innovation is needed to develop programming systems that can harness the potential parallelism of FPGAs.

Another place where fundamentally different approaches may be needed is alternatives to CMOS. There are many advantages to sticking with today's silicon-based CMOS technology, which has proved remarkably scalable over many generations of microprocessors and around which an enormous industrial and experience base has been established. However, it will also be essential to invest in new computation substrates whose underlying power efficiency promises to be fundamentally better than that of silicon-based CMOS circuits. Computing has benefited in the past from order-of-magnitude performance improvements in power consumption in the progression from vacuum tubes to discrete bipolar transistors to integrated circuits first based on bipolar transistors, then on N-type metal oxide semiconductors (NMOS) and now on CMOS. No alternative is near commercial availability yet, although some show potential.

In the best case, investment will yield devices and manufacturing methods—as yet unforeseen—that will dramatically surpass the CMOS IC. In the worst case, no new technology will emerge to help solve the problems. That uncertainty argues for investment in multiple approaches as soon as possible, and computer system designers would be well advised not to expect one of the new devices to appear in time to obviate the development of new, parallel architectures built on the proven CMOS technology. Better performance is needed immediately. Society cannot wait the decade or two that it would take to identify, refine, and apply a new tech-

16

nology that may or may not even be on the horizon now. Moreover, even if a groundbreaking new technology were discovered, the investment in parallelism would not be wasted, in that advances in parallelism would probably exploit the new technology as well.

Recommendation: Invest in research and development to make computer systems more power-efficient at all levels of the system, including software, application-specific approaches, and alternative devices. Such efforts should address ways in which software and system architectures can improve power efficiency, such as by exploiting locality and the use of domain-specific execution units. R&D should also be aimed at making logic gates more power-efficient. Such efforts should address alternative physical devices beyond incremental improvements in today's CMOS circuits.

Because computing systems are increasingly limited by energy consumption and power dissipation, it is essential to invest in research and development to make computing systems more power-efficient. Exploiting parallelism alone cannot ensure continued growth in computer performance. There are numerous potential avenues for investigation into better power efficiency, some of which require sustained attention to known engineering issues and others of which require research. These include:

- Redesign the delivery of power to and removal of heat from computing systems for increased efficiency. Design and deploy systems in which the absolute maximum fraction of power is used to do the computing and less is used in routing power to the system and removing heat from the system. New voluntary or mandatory standards (including ones that set ever-more-aggressive targets) might provide useful incentives for the development and use of better techniques.

- Develop alternatives to the general-purpose processor that exploit locality.

- Develop domain-specific or application-specific processors analogous to GPUs and DSPs that provide better performance and power-consumption characteristics than do general-purpose processors for other specific application domains.

- Investigate possible new, lower-power device technology beyond CMOS.

Additional research should focus on system designs and software configurations that reduce power consumption, for example, reducing

power consumption when resources are idle, mapping applications to domain-specific and heterogeneous hardware units, and limiting the amount of communication among disparate hardware units.

Although the shift toward CMPs will allow industry to continue for some time to scale the performance of CMPs based on general-purpose processors, general-purpose CMPs will eventually reach their own limits. CMP designers can trade off single-thread performance of individual processors against lower energy dissipation per instruction, thus allowing more instructions by multiple processors while the same amount of energy is dissipated by the chip. However, that is possible only within a limited range of energy performance. Beyond some limit, lowering energy per instruction by processor simplification can lead to degradation in overall CMP performance because processor performance starts to decrease faster than energy per instruction. When that occurs, new approaches will be needed to create more energy-efficient computers.

It may be that general-purpose CMPs will prove not to be a solution in the long run and that we will need to create more applicationoptimized processing units. Tuning hardware and software toward a specific type of application allows a much more energy-efficient solution. However, the current design trend is away from building customized solutions, because increasing design complexity has caused the nonrecurring engineering costs for designing the chips to grow rapidly. High costs limit the range of potential market segments to the few that have volume high enough to justify the initial engineering investment. A shift to more application-optimized computing systems, if necessary, demands a new approach to design that would allow application-specific chips to be created at reasonable cost.

### **Recommendations for Practice and Education**

Implementing the research agenda proposed here, although crucial for progress, will take time. Meanwhile, society has an immediate and pressing need to use current and emerging CMP systems effectively. To that end, the committee offers three recommendations related to current development and engineering practices and educational opportunities.

## Recommendation: To promote cooperation and innovation by sharing, encourage development of open interface standards for parallel programming rather than proliferating proprietary programming environments.

Private-sector firms are often incentivized to create proprietary interfaces and implementations to establish a competitive advantage. How-

ever, a lack of standardization can impede progress inasmuch as the presence of many incompatible approaches allows none to achieve the benefits of wide adoption and reuse—a major reason that industry participates in standards efforts. The committee encourages the development of programming-interface standards that can facilitate wide adoption of parallel programming even as they foster competition in other matters.

# Recommendation: Invest in the development of tools and methods to transform legacy applications to parallel systems.

Whatever long-term success is achieved in the effective use of parallel systems from rethinking algorithms and developing new programming methods will probably come at the expense of the backward-platform and cross-platform compatibility that has been an economic cornerstone of IT for decades. To salvage value from the nation's current, substantial IT investment, we should seek ways to bring sequential programs into the parallel world. On the one hand, there are probably no "silver bullets" that enable automatic transformation. On the other hand, it is prohibitively expensive to rewrite many applications. The committee urges industry and academe to develop "power tools" for experts that can help them to migrate legacy code to tomorrow's parallel computers. In addition, emphasis should be placed on tools and strategies to enhance code creation, maintenance, verification, and adaptation of parallel programs.

### Recommendation: Incorporate in computer science education an increased emphasis on parallelism, and use a variety of methods and approaches to better prepare students for the types of computing resources that they will encounter in their careers.

Who will develop the parallel software of the future? To sustain IT innovation, we will need a workforce that is adept in writing parallel applications that run well on parallel hardware, in creating parallel software systems, and in designing parallel hardware.

Both undergraduate and graduate students in computer science, as well as in other fields that make intensive use of computing, will need to be educated in parallel programming. The engineering, science, and computer-science curriculum at both the undergraduate and graduate levels should begin to incorporate an emphasis on parallel computational thinking, parallel algorithms, and parallel programming. With respect to the computer-science curriculum, because no general-purpose paradigm has emerged, universities should teach diverse parallel-programming languages, abstractions, and approaches until effective ways of teaching 20

and programming emerge. The necessary shape of the needed changes will not be clear until some reasonably general parallel-programming methods have been devised and shown to be promising.

Related to this is improving the ability of the programming workforce to cope with the new challenges of parallelism. This will involve retraining today's programmers and also developing new models and abstractions to make parallel programming more accessible to typically skilled programmers.

### CONCLUDING REMARKS

There is no guarantee that we can make future parallel computing ubiquitous and as easy to use as yesterday's sequential computer, but unless we aggressively pursue efforts as suggested by the recommendations above, it will be game over for future growth in computing performance. This report describes the factors that have led to limitations of growth of single processors based on CMOS technology. The recommendations here are aimed at supporting and focusing research, development, and education in architectures, power, and parallel computing to sustain growth in computer performance and to permit society to enjoy the next level of benefits. 1

# The Need for Continued Performance Growth

Information technology (IT) has become an integral part of modern society, affecting nearly every aspect of our lives, including education, Lendicine, government, business, entertainment, and social interactions. Innovations in IT have been fueled by a continuous and extraordinary increase in computer performance. By some metrics computer performance has improved by a factor of an average of 10 every 5 years over the past 2 decades. A sustained downshift in the rate of growth in computing performance would have considerable ramifications both economically and for society. The industries involved are responsible for about \$1 trillion of annual revenue in the United States. That revenue has depended on a sustained demand for IT products and services that in turn has fueled demand for constantly improving performance. Indeed, U.S. leadership in IT depends in no small part on its driving and taking advantage of the leading edge of computing performance. Virtually every sector of society-manufacturing, financial services, education, science, government, military, entertainment, and so on-has become dependent on the continued growth in computing performance to drive new efficiencies and innovations. Moreover, all the current and foreseeable future applications rely on a huge software infrastructure, and the software infrastructure itself would have been impossible to develop with the more primitive software development and programming methods of the past. The principal force allowing better programming models, which emphasize programmer productivity over computing efficiency, has been the

growth in computing performance. (Chapter 4 explores implications for software and programming in more detail.)

This chapter first considers the general question of why faster computers are important. It then examines four broad fields—science, defense and national security, consumer applications, and enterprise productivity—that have depended on and will continue to depend on sustained growth in computing performance. The fields discussed by no means constitute an exhaustive list,<sup>1</sup> but they are meant to illustrate how computing performance and its historic exponential growth have had vast effects on broad sectors of society and what the results of a slowdown in that growth would be.

## WHY FASTER COMPUTERS ARE IMPORTANT

Computers can do only four things: they can move data from one place to another, they can create new data from old data via various arithmetic and logical operations, they can store data in and retrieve them from memories, and they can decide what to do next. Students studying computers or programming for the first time are often struck by the surprising intuition that, notwithstanding compelling appearance to the contrary, computers are extremely primitive machines, capable of performing only the most mind-numbingly banal tasks. The trick is that computers can perform those simple tasks extremely fast—in periods measured in billionths of a second—and they perform these tasks reliably and repeatably. Like a drop of water in the Grand Canyon, each operation may be simple and may in itself not accomplish much, but a lot of them (billions per second, in the case of computers) can get a lot done.

Over the last 60 years of computing history, computer buyers and users have essentially "voted with their wallets" by consistently paying more for faster computers, and computer makers have responded by pric-

<sup>&</sup>lt;sup>1</sup>Health care is another field in which IT has substantial effects—in, for example, patient care, research and innovation, and administration. A recent National Research Council (NRC) report, although it does not focus specifically on computing performance, provides numerous examples of ways in which computation technology and IT are critical underpinnings of virtually every aspect of health care (NRC, 2009, Computational Technology for Effective Health Care: Immediate Steps and Strategic Directions, Washington, D.C.: The National Academies Press, available online at http://www.nap.edu/catalog.php?record\_id=12572). Yet another critically important field that increasingly benefits from computation power is infrastructure. "Smart" infrastructure applications in urban planning, high-performance buildings, energy, traffic, and so on are of increasing importance. That is also the underlying theme of two of the articles in the February 2009 issue of Communications of the ACM (Tom Leighton, 2009, Improving performance on the Internet, Communications of the ACM 52(2): 44-51; and T.V. Raman, 2009, Toward 2<sup>W</sup>: Beyond Web 2.0, Communications of the ACM 52(2): 52-59).

ing their systems accordingly: a high-end system may be, on the average, 10 percent faster and 30 percent more expensive than the next-best. That behavior has dovetailed perfectly with the underlying technology development in the computers—as ever-faster silicon technology has become available, faster and faster computers could be designed. It is the nature of the semiconductor manufacturing process that silicon chips coming off the fabrication line exhibit a range of speeds. Rather than discard the slower chips, the manufacturer simply charges less for them. Ever-rising performance has been the wellspring of the entire computer industry. Meanwhile, the improving economics of ever-larger shipment volumes have driven overall system costs down, reinforcing a virtuous spiral<sup>2</sup> by making computer systems available to lower-price, larger-unit-volume markets.

For their part, computer buyers demand ever-faster computers in part because they believe that using faster machines confers on them an advantage in the marketplace in which they compete.<sup>3</sup> Applications that run on a particular generation of computing system may be impractical or not run at all on a system that is only one-tenth as fast, and this encourages hardware replacements for performance every 3-5 years. That trend has also encouraged buyers to place a premium on fast new computer systems because buying fast systems will forestall system obsolescence as long as possible. Traditionally, software providers have shown a tendency to use exponentially more storage space and central processing unit (CPU) cycles to attain linearly more performance; a tradeoff commonly referred to as bloat. Reducing bloat is another way in which future system improvements may be possible. The need for periodic replacements exists whether the performance is taking place on the desktop or in the "cloud"

<sup>&</sup>lt;sup>2</sup>A small number of chips are fast, and many more are slower. That is how a range of products is produced that in total provide profits and, ultimately, funding for the next generation of technology. The semiconductor industry is nearing a point where extreme ultraviolet (EUV) light sources—or other expensive, exotic alternatives—will be needed to continue the lithography-based steps in manufacturing. There are a few more techniques left to implement before EUV is required, but they are increasingly expensive to use in manufacturing, and they are driving costs substantially higher. The future scenario that this implies is not only that very few companies will be able to manufacture chips with the smallest feature sizes but also that only very high-volume products will be able to justify the cost of using the latest generation of technology.

<sup>&</sup>lt;sup>3</sup>For scientific researchers, faster computers allow larger or more important questions to be pursued or more accurate answers to be obtained; office workers can model, communicate, store, retrieve, and search their data more productively; engineers can design buildings, bridges, materials, chemicals, and other devices more quickly and safely; and manufacturers can automate various parts of their assembly processes and delivery methods more costeffectively. In fact, the increasing amounts of data that are generated, stored, indexed, and retrieved require continued performance improvements. See Box 1.1 for more on data as a performance driver.

#### BOX 1.1 Growth of Stored and Retrievable Data

The quantity of information and data that is stored in a digital format has been growing at an exponential rate that exceeds even the historical rate of growth in computing performance, which is the focus of this report. Data are of value only if they can be analyzed to produce useful information that can be retrieved when needed. Hence, the growth in stored information is another reason for the need to sustain substantial growth in computing performance.

As the types and formats of information that is stored in digital form continue to increase, they drive the rapid growth in stored data. Only a few decades ago, the primary data types stored in IT systems were text and numerical data. But images of increasing resolution, audio streams, and video have all become important types of data stored digitally and then indexed, searched, and retrieved by computing systems.

The growth of stored information is occurring at the personal, enterprise, national, and global levels. On the personal level, the expanding use of e-mail, text messaging, Web logs, and so on is adding to stored text. Digital cameras have enabled people to store many more images in their personal computers and data centers than they ever would have considered with traditional film cameras. Video cameras and audio recorders add yet more data that are stored and then must be indexed and searched. Embedding those devices into the ubiquitous cell phone means that people can and do take photos and movies of events that would previously not have been recorded.

At the global level, the amount of information on the Internet continues to increase dramatically. As static Web pages give way to interactive pages and social-networking sites support video, the amount of stored and searchable data continues its explosive growth. Storage technology has enabled this growth by reducing the cost of storage by a rate even greater than that of the growth in processor performance.

The challenge is to match the growth in stored information with the computational capability to index, search, and retrieve relevant information. Today, there are not sufficiently powerful computing systems to process effectively all the images and video streams being stored. Satellite cameras and other remote sensing devices typically collect much more data than can be examined for useful information or important events.

Considerably more progress is needed to achieve the vision described by Vannevar Bush in his 1945 paper about a MEMEX device that would collect and make available to users all the information relevant to their life and work.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Vannevar Bush, 1945, "As we may think," Atlantic Magazine, July 1945, available online at http://www.theatlantic.com/magazine/archive/1969/12/as-we-may-think/3881/.

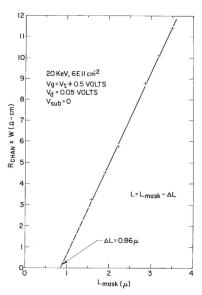

in a Web-based service, although the pace of hardware replacement may vary in the cloud.